alarm clock

$10-30 USD

Ολοκληρώθηκε

Αναρτήθηκε περίπου 9 χρόνια πριν

$10-30 USD

Πληρωμή κατά την παράδοση

Design the control logic for an alarm clock (for simulation purposes 20ns simulation = 1 minute real time – this can be adjusted somewhat for simulation purposes).

a) Use multiple input signals (alarm set input, the snooze, and the alarm time).

b) The design will contain one output (Alarm_On). A logic high at the output represents the alarm being “on”.

c) An input will be used to set the alarm off.

d) When the simulation starts, a counting mechanism will start counting (representing/roughly simulating a clock).

e) If the alarm set input signal is high, then the alarm should turn on when the count equals the preset alarm value. If at any point during the simulation the alarm set input is switched off, the alarm should turn off by the next complete clock cycle.

f) If the snooze button is activated (assume that snooze is a pulse that is at least one full clock cycle in duration) the alarm should turn off and then turn back on after 5 minutes.

g) Repeat snooze button simulations (pulses) should cause the same behavior in the circuit.

h) If at any time the alarm set input signal goes low, the Alarm_On output should go low by the end of the next complete clock cycle.

i) Clearly describe any additional rules or assumptions.

Write a VHDL or Verilog code that implements the above alarm clock. Use one-hot encoding for state encoding. Verify the functionality and behavior of the circuit. Use Quartus II toolset. Submit a report containing the following:

1. A state diagram showing the implementation of your design (overview of your design, a detailed description of your approach and design process). Clearly show all the states and the conditions on which transitions occur.

2. Hardcopy of your code.

3. Hardcopy of annotated (properly labeled) waveforms that demonstrate all the required behavior.

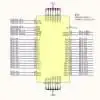

4. RTL schematic of the design after compilation.

5. Roughly, draw the implied hardware of your code. Provide a brief comparison between the tool's RTL schematic and the implied hardware you drew.

6. Extract the highest clock frequency of your design from the compilation report.

Ταυτότητα εργασίας: 7450047

Σχετικά με την εργασία

8 προτάσεις

Απομακρυσμένη Εργασία

Ενεργός/ή 9 χρόνια πριν

Ψάχνεις τρόπο για να κερδίσεις μερικά χρήματα;

Πλεονεκτήματα πλειοδοσίας στο Freelancer

Καθόρισε τον προϋπολογισμό σου και το χρονοδιάγραμμα

Πληρώσου για τη δουλειά σου

Περίγραψε την πρόταση σου

Η εγγραφή και η πλειοδοσία σε εργασίες είναι δωρεάν

8 freelancers δίνουν μια μέση προσφορά $29 USD για αυτή τη δουλειά

7,8

7,8

5,8

5,8

5,1

5,1

2,1

2,1

0,0

0,0

0,0

0,0

0,0

0,0

Σχετικά με τον πελάτη

Bridgeport, United States

1

Επαληθευμένη μέθοδος πληρωμής

Μέλος από Μαρ 13, 2015

Επαλήθευση Πελάτη

Άλλες δουλειές από αυτόν τον πελάτη

$10-30 USD

$10-30 USD

Παρόμοιες εργασίες

$30-250 USD

min €36 EUR / hour

$10-65 USD

$30-250 USD

min €36 EUR / hour

$10-60 USD

$10-65 USD

$10-60 USD

$30-250 USD

min €36 EUR / hour

$10-65 USD

$10-60 USD

Ευχαριστούμε! Σου έχουμε στείλει ένα email με ένα σύνδεσμο για να διεκδικήσεις τη δωρεάν πίστωση σου.

Κάτι πήγε στραβά κατά την προσπάθεια αποστολής του email σου. Παρακαλούμε δοκίμασε ξανά.

Φόρτωση προεπισκόπησης

Δόθηκε πρόσβαση για Geolocation.

Η σύνδεση σου έχει λήξει και τώρα έχεις αποσυνδεθεί. Παρακαλούμε συνδέσου ξανά.